지난해 자일링스는 통합 소프트웨어 개발 플랫폼 바이티스(Vitis)를 내놓으면서 프로그래머블반도체(FPGA) 역사에 한 획을 그었다.

바이티스(Vitis)는 범용 C언어 등으로 소프트웨어는 물론 FPGA 하드웨어 설계까지 할 수 있는 종합 개발 환경(IDE)이다. 5년에 걸쳐 개발된 이 플랫폼으로 자일링스는 FPGA 생태계를 둘러싸고 있던 진입 장벽을 무너뜨렸다.

자일링스는 왜 생태계의 장벽을 허물었을까. 그리고 바이티스의 등장은 FPGA 업계에 어떤 영향을 미칠까.

변화는 그 전부터 시작됐다

하드웨어 업체인 자일링스가 하드웨어가 아닌 소프트웨어 역량을 내세우기 시작한 건 지난 2011년부터다. 반도체 설계 엔지니어들도 어려워하는 FPGA 프로그래밍 언어 대신 범용 프로그래밍 언어로 FPGA와 소프트웨어를 함께 개발할 수 있게 하겠다는 게 최종 목표였다.

그 전까지만 해도 FPGA는 ‘하드웨어 프로그래머블’에 머물러 있었다. 자일링스가 하드웨어 기능 구현(HDL)을 위한 레지스터 트랜스퍼 레벨(RTL) 툴을 제공하면, 고객사는 이를 활용해 RTL 설계를 한 다음 소프트웨어를 따로 개발해서 결합해야했다.

2011년, 자일링스는 ‘올 프로그래머블’ 개념을 도입했다. 올 프로그래머블은 하드웨어는 물론 소프트웨어 설계까지 하나의 개발 환경에서 진행할 수 있는 FPGA다.

그 해, 자일링스는 시스템온칩(SoC) 형태의 징크(Zynq) 제품군과 C언어로 소프트웨어를 개발해 FPGA에 올릴 수 있는 비바도(Vivado) HLS(High Level Synthesis) 개발 도구를 내놓으며 임베디드 개발 장벽부터 허물었다.

지난 2014년, 또 한 번의 변화가 일어났다. 자일링스는 2014년 3월부터 이듬해 3월까지 소프트웨어 정의 개발 툴 시리즈 ‘SDx’ 3종을 연달아 출시했다. 프로그래밍 언어는 C언어에서 오픈CL, C++로 확장됐고, SoC에 여러 기능이 추가되면서 ‘멀티 프로세싱(MP)’이라는 수식어가 붙었다.

당시 스티브 글레이저 자일링스 수석부사장은 한 언론사와의 인터뷰에서 “각종 통신 장비가 서로 연결되는 5세대 이동통신(5G)에 대한 연구개발(R&D)이 활발해지면서 소프트웨어로 모든 것을 해결하고자 하는 고객 수요가 늘어났다”며 “프로그래머블은 이제 하드웨어에만 국한된 게 아니다”고 개발 배경을 설명했다.

지난해 바이티스(Vitis)로 변화는 정점을 찍었다.

지난해 11월부터 무료 공개된 바이티스 플랫폼은 C, C++는 물론 인공지능(AI) 개발자들이 주로 쓰는 파이썬(Python) 언어까지 포괄적으로 지원한다. 각종 설계자산(IP) 라이브러리가 각 응용처별로 마련됐다.

일부 유료인데다 다른 소프트웨어 개발 환경(SDE)이나 통합개발환경(IDE)에 연결해야하는 비바도와 달리, 바이티스는 그냥 ‘바이티스’ 하나만 있어도 프로그래밍이 가능하다. 소프트웨어 개발자가 원하는 IDE에 연결해 사용하는 것도 된다.

라민 론 자일링스 소프트웨어 및 AI 제품 관리 담당 부사장은 지난해 ‘자일링스 개발자 포럼(XDF) 2019’에서 “비바도 등 기존 개발 도구 역시 훌륭했지만, 여전히 하드웨어 설계에는 박사급 인력이 필요하다”며 “비바도보다 사용하기 쉬운 개발 환경에 대한 요구가 컸고, 5년 전부터 개발에 돌입했다”고 말했다.

소프트웨어 개발자들은 왜 FPGA 장벽을 허물어달라고 요구했을까

사실 반도체 업계에도 FPGA는 특수 영역이다.

FPGA 프로그래밍 언어는 VHDL(Very high speed integrated circuit HDL)과 베릴로그(Verilog) HDL로 나뉜다. VHDL은 상위 동작 단계부터 하위 게이트 레벨까지 폭넓은 범위에 활용할 수 있다. CAD 업계 및 IEEE 표준 언어지만, 실제 언어를 이해하고 원활히 사용하는 데 많은 시간과 노력이 든다.

이에 업계는 C 언어와 유사한 베릴로그 HDL을 활용해 FPGA를 개발해왔다. 하지만 베릴로그 HDL을 쓰면, VHDL만큼 광범위한 영역을 건드릴 수 없어 하드웨어의 성능을 100% 활용하기가 어려웠다.

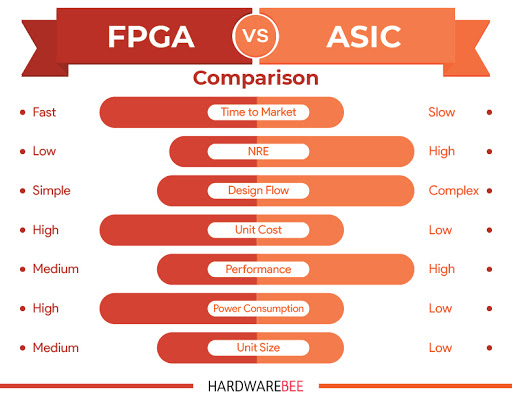

업계 관계자는 “FPGA 설계는 특히 엔지니어의 노하우가 중요하다”며 “보통 반도체 설계 업체들도 60~70% 성능을 뽑아내서 FPGA를 만들어보고, 그 다음 전용반도체(ASIC)로 넘어간다”고 설명했다.

하드웨어 개발자들도 아닌 소프트웨어 개발자들이 FPGA를 탐내기 시작한 건 불과 5~6년 전이다. 구글을 필두로 인공지능(AI)과 자율주행에 대한 연구개발(R&D)이 가속화되고, 5세대 이동통신(5G) 표준화 작업이 시작됐던 시기다.

AI는 어쨌거나 소프트웨어 알고리즘이다. 따라서 AI를 개발하는 건 하드웨어 개발자가 아닌 소프트웨어 개발자다. 이들의 고민은 자신들이 만든 AI 알고리즘을 담을 수 있는, 충분한 성능을 가진 하드웨어를 찾는 것이었다.

지금이야 AI 가속기 시장이 주목받고 있지만, 그때까지만 해도 AI 하드웨어는 그래픽처리장치(GPU)가 전부였다. 비용도 비용인데다 수요 폭증으로 공급도 잘 되지 않는 GPU를 전면 채택하기엔 부담이 컸다.

그렇다고 직접 ASIC을 개발하기도 쉽지 않았다. ASIC을 개발하려면 별도 하드웨어 엔지니어를 뽑아야했고, 개발 기간도 기본 2년은 잡아야했다. 알고리즘의 밑바탕이 되는 프레임워크도 유행을 타는 상황이라, 한번 양산하면 기능을 바꿀 수 없는 ASIC은 부담이 컸다.

5G도 비슷했다. 소프트웨어 가상화 네트워크(SVN)가 선택 사항이었던 4G와 달리 5G는 이 기능이 기본으로 들어간다. 이동통신 서비스를 기존 모바일 기기를 넘어 각 산업별로 특화시켜 제공하기 위해서다.

이를 구현하려면 무엇보다 소프트웨어 개발 역량을 보강해야했다. 4G까지는 소프트웨어가 내장된 장비를 사다 쓰면 그만이었지만, 이제는 장비만 사고 각 통신사가 입맛에 맞는 소프트웨어를 개발해 올리는 게 대세가 됐다. 이들도 AI 개발자들과 같은 고민에 빠졌다.

그래서 주목받은 게 FPGA다. FPGA는 빠르면 3개월 안에 개발이 끝난다. 개발 후에도 기능 조정이 가능했고, 걸림돌인 개발 환경만 소프트웨어 친화적으로 바뀐다면 가용성도 문제 없었다. 전력소모량 대비 성능(전성비)도 GPU에 밀리지 않았다.

바이티스로 FPGA 역사는 어떻게 바뀔까

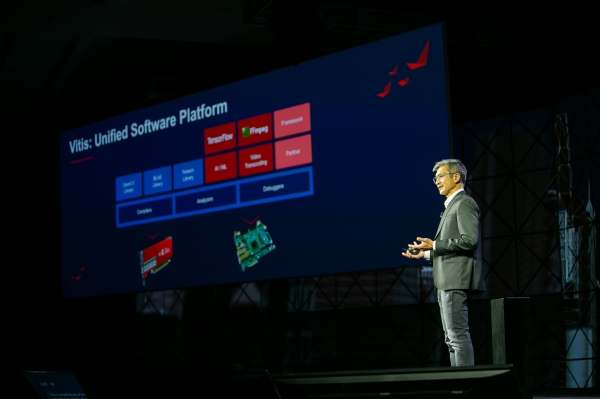

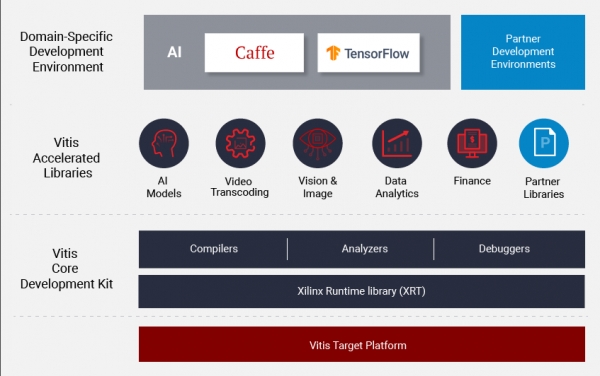

바이티스 플랫폼은 특정 기능에 최적화된 도메인 특화 아키텍처(DSA) 개발에 최적화된 개발 환경이다.

소프트웨어 개발자는 애플리케이션 프로그래밍 인터페이스(API)를 통해 사전 정의된 이들 라이브러리를 불러와 활용할 수 있다. 반대로 하드웨어 개발자들은 만들어놓은 하드웨어 모듈을 소프트웨어 API로 불러와 집어넣을 수 있다.

x86 아키텍처는 물론 Arm 호환 CPU 코어도 프로그래밍 가능하다. 소프트웨어와 하드웨어의 경계는 물론, 아키텍처의 경계도 없앤 셈이다.

바이티스 플랫폼에서는 ▲선형대수하위프로그램(BLAS) ▲해석(Solver) ▲보안(Security) ▲비전(Vision) ▲데이터압축(Compression) ▲검증(Quality) ▲금융(Quantitative Finance) ▲데이터베이스(Database)를 포함, 총 8개의 가속화 전용 라이브러리를 오픈소스로 지원한다.

AI를 위한 ‘바이티스AI’도 지난해 12월부터 서비스를 시작했다. 바이티스AI를 활용하면 텐서플로(TensorFlow), 카페(Caffe) 등 AI 오픈 프레임워크를 그대로 갖다 써서 자일링스 제품 내 AI 엔진을 프로그래밍할 수 있다.

보통 AI 알고리즘은 개발 초기 고정밀 부동 소수점을 기반으로 학습되는데, 바이티스AI는 이를 현장에 배포하기 쉽도록 네트워크를 병렬화하고 필요없는 부분을 잘라내 공간 및 전력 효율성을 최적화하도록 도와준다.

개발자 커뮤니티도 대폭 개편했다. 자일링스 개발자 사이트의 첫 화면은 AI 추론, 자동차, 통신, 데이터베이스 및 분석, 금융, 고성능컴퓨팅(HPC) 등 원하는 응용처를 택하는 것으로 시작된다.

작년 10월, 바이티스를 공개하면서 문을 연 이 사이트는 초기 알베오(Alveo) 활용에 대한 글만 올라왔지만 이동통신 트랜시버, 보안, 빔포밍 등 다양한 기술에 관한 글도 추가 게재됐다. 개발자들이 서로 의견을 나누는 포럼(Forum) 카테고리도 지난 2일 하루에만 50여개의 질문이 올라오는 등 활발하게 돌아가고 있다.

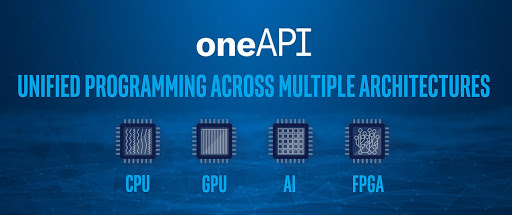

바이티스에 대한 반응은 뜨거웠다. 가장 먼저 반응한 건 FPGA 업계 2위 알테라를 인수한 인텔이다. 인텔은 자일링스가 바이티스를 발표한 지 한 달여 뒤 ‘원(one) API’를 공개했다.

원 API는 C++ 언어 기반인 DPC++(Data Parallel C++) 프로그래밍 언어를 활용해 CPU, GPU, FPGA는 물론 기타 하드웨어 가속기까지 개발할 수 있는 도구다. 직접 프로그래밍 및 API 기반 프로그래밍을 지원한다.

업계 관계자는 “반도체 설계는 더 이상 하드웨어 엔지니어들만의 과제가 아니다”며 “엔비디아, 자일링스, 인텔 모두 소프트웨어 기반 개발 환경(IDE)을 보강하기 시작하면서 소프트웨어와 하드웨어간 경계는 지속적으로 흐려질 것”이라고 말했다.